1.はじめに

システム設計やレイアウトの考え方を中心に説明いたします

この連載では、システム設計とレイアウトの考え方や、新しい技術の紹介などを中心にいくつかの大きな項目について説明していきます。この講座では、ある程度、回路や解析の知識がある方を対象としているため、専門用語や概念が説明無しに出てきます。用語が分からない方は、メールでお問い合わせいただくか、本サイト内の他の講座を合わせてお読みください。

高速システムでは、論理回路設計とレイアウト設計の関係は、これまでのデジタル回路設計に比べて、ずっと密接に関連するようになっています。

そして、論理回路設計とレイアウト設計の間を密接に接続する接着剤として、伝送線路解析があります。

最近では、これにIC設計までを含めた、協調設計の必要性が話題になっていますが、ここでも、論理設計と基板設計、IC設計、ICパッケージ設計を結び付けているのは、PI解析を含めた「PI, SI解析」です。SIやPIについては、いずれ、「GHz信号の解析講座」で詳しく説明します。

この連載の目的は、このSI技術を中心に、論理回路設計とレイアウト設計の関係を説明していくことです。

最初のテーマとして、クロッック回路の回路設計とレイアウト設計について、何回かにわたって紹介していきます。

2.同期回路と非同期回路

システムにクロックは不可欠なものです。CPUは全て、クロックを基本に動作し、このクロックのスピードがCPUの性能の指針となっているほどです。

つまり、「1.8ギガチップより2.4ギガチップの方が高速だ」、などです。また、メモリーシステムも全てDDR-2 800とかDDR-2 533などのように、クロックで表しています。PCI-33やPCI-66もクロック速度です。

しかし、デジタルシステムの中には、全くクロックの無いシステムも存在します。例えば、ルームエアコンや冷蔵庫のコントローラを考えます。

ルームエアコンで例えてみると・・・

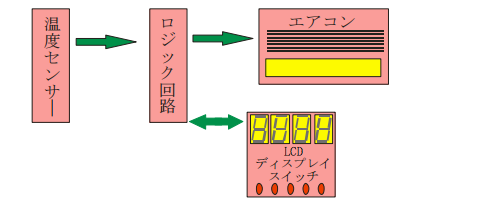

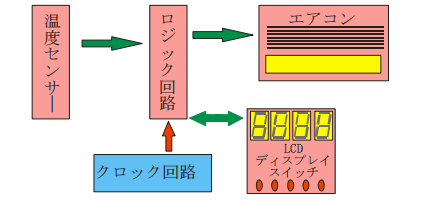

温度設定ボタンで、温度を設定するとその温度はコントローラの液晶に表示されます。温度センサーから入力した温度と設定温度を比較して、設定温度の方が低ければ、冷房をONにします。

設定温度の方が高ければ、冷房をOFFにします。

外気温度が変化すれば、その都度、センサーからの入力データが変化して、システムが動作します。

このような回路では、クロックは使わないで、以下の図のような回路を組むことができます。

実際には、エアコンや冷蔵庫のコントローラでもマイコンを組み込んでクロックを使って動作しています。

クロックの無い非同期回路など、特殊な回路のように思われるかも知れませんが、実は、DDRやSDR以前のメモリーシステムではクロック信号は使われていません。

SDRメモリーでは、クロック信号で同期させることから、「同期式メモリー(Synchronous Dynamic RAM)」と呼ばれています。

このように、クロックを使わないで動作するデジタル回路を非同期回路(Asynchronous Circuit)と呼びます。

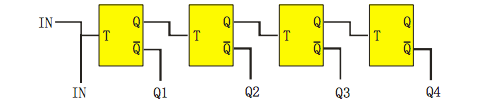

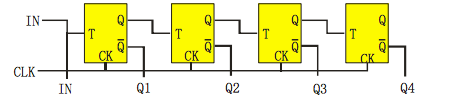

例えば、以下の図のようなFlip Flop(FF)によるカウンタ回路を考えます。

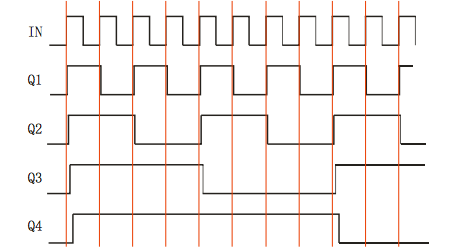

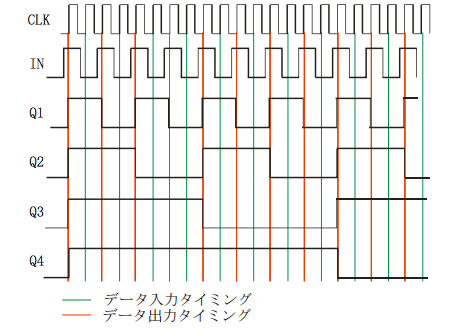

このFFはT入力の立下りエッジで、Q、-Q出力を反転させます。つまり、最初のFFのInputに32のパルスが入力されると、最初のQ1出力は16パルス、次のFFのQ2出力には8パルス、Q3出力には4パルスの信号が出力されます。

つまり、1つのFFで、パルスの数が1/2になる、バイナリカウンタ回路になっています。

ここで問題は、FF1の入力に対して、FF1の出力は、FFの内部の回路動作時間だけ遅れて出力されます。FF2の出力はFF1の入力に対して、FF2個分の遅れの後、データが出力されます。

後のFFになるに従って、データ出力のタイミングが遅くなってきます。

非同期回路では、データの入力、出力タイミングは少しずつ違っています。データを読む時には、全てのデータが出揃った時を見計らって読み込むとか、エアコンのセンサーのように、いつでも、データが変化した時に読み込むなどの回路が必要です。

しかし、システムが高速になると、全てのデータが出揃った時まで、待ってからデータを読み込むのでは、回路の動作は、最も遅い回路に余裕を持たせた遅い速度で動作しないと、安定した動作が保てません。

それに対して、一般の回路のようにクロック信号を使い、全ての素子が、クロック信号を基に動作するようにすれば、クロックの速度で、回路が動作できます。この様なクロックを基準に動作する回路を同期回路(Synchronous Circuit)と呼びます。

最近はクロックで動作する回路ですが、システム全体が統合したクロックで動作するのではなく、小さな回路ブロックや、相互接続しているIC間だけでローカルなクロックを使って動作するような回路を非同期回路(Clockless Circuit) と呼ぶこともあります。

3.同期回路

次に先ほどのFFを使った非同期回路を同期回路で組んで見ましょう。

このFFはClk入力端子を持ちClk信号の立ち下りエッジで、T端子のデータを読み込み、Clk信号の立ち上りエッジで、読み込んだデータを出力します。

この回路では、全てのFFがClk信号の立ち下りから同じ時間の遅延でデータを出力します。

このようにすれば、Clk信号の立ち上りエッジで全てのFFの出力データを読み込めば、必ず正しいデータが読み込めます。例え、データの入力(INPUT)がどのタイミングで入力されても、FFの出力、Q1, Q2, Q3, Q4は全て同じタイミングで出力されます。

クロック信号のタイミングで、非常に高速で回路を動作させても、正しいデータが読めることになります。このように、同期回路では、非同期回路より、回路の高速動作が可能となります。

このため、現在の高速回路では、クロック信号を使った同期方式の回路が主流で、クロック信号は、回路全体の動作を制御する非常に重要な信号となっています。

4.遅くても恐ろしいクロック信号

クロック信号はシステムの動作を制御する基本信号です。全てのICはクロック信号に同期して動作します。このため、クロック信号が、誤動作したりノイズで正確に伝わらなかったりすると、システム全体が誤動作して、動作しなくなります。

クロックは高速クロックはもちろんですが、例え、遅い信号でも必ずシミュレーションして、きちんと波形歪みが無く、正しいタイミングで、他のICやコネクタに伝わっていることを確認します。

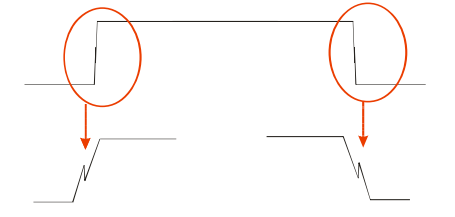

遅いクロック信号で、よく発生するトラブルに、グリッチがあります。これは、クロック信号の立ち上り、立ち下りの途中、スレッショルドレベル付近で、信号にリングバックなどのノイズが発生して、瞬間的にクロックがON, OFFして、誤動作するものです。

特に遅いクロック信号では、シミュレーションでも、立ち上り、立ち下りの途中のバウンスを見落とすことがありますので注意しましょう。